Product Summary

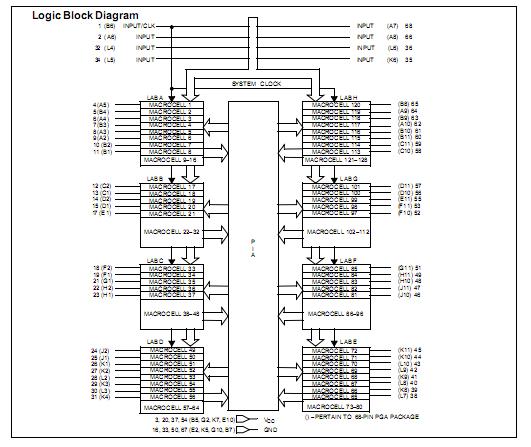

The CY7C342B-35RI is an Erasable Programmable Logic Device(EPLD) in which CMOS EPROM cells are used to configure logic functions within the device. The 128 macrocells in the CY7C342B-35RI are divided into eight LABs, 16 per LAB. There are 256 expander product terms, 32 per LAB, to be used and shared by the macrocells within each LAB. The speed and density of the CY7C342B-35RI allows it to be used in a wide range of applications, from replacement of large amounts of 7400-series TTL logic, to complex controllers and multifunction chips. Each LAB is interconnected with a programmable interconnect array, allowing all signals to be routed throughout the chip.

Parametrics

CY7C342B-35RI absolute maximum ratings: (1)Storage Temperature:–65℃ to +135℃; (2)Ambient Temperature with Power Applied:–65℃ to +135℃; (3)Maximum Junction Temperature(under bias):150℃; (4)Supply Voltage to Ground Potential:–2.0V to +7.0V; (5)DC Output Current per Pin:–25 mA to +25 mA; (6)DC Input Voltage:–2.0V to +7.0V.

Features

CY7C342B-35RI features: (1)128 macrocells in eight logic array blocks (LABs); (2)Eight dedicated inputs, 52 bidirectional I/O pins; (3)Programmable interconnect array; (4)Advanced 0.65-micron CMOS technology to increase performance ; (5)Available in 68-pin HLCC, PLCC, and PGA packages.

Diagrams

|

CY7C006 |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A |

Other |

|

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-15AXCT |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AC |

|

IC SRAM 16KX8 DUAL 64LQFP |

Data Sheet |

Negotiable |

|

||||||||||||

|

CY7C006A-20AXC |

Cypress Semiconductor |

SRAM 5V 16Kx8 COM Dual Port SRAM |

Data Sheet |

|

|

||||||||||||

(China (Mainland))

(China (Mainland))